PERCOBAAN 2a

1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

- Panel DL 2203D

- Panel DL 2203S

- Panel DL 2203C

- Jumper

3. Rangkaian Simulasi [Kembali]

4. Prinsip Kerja Rangkaian [Kembali]

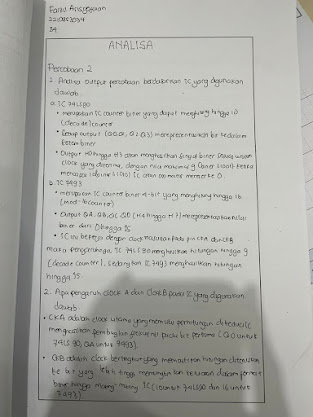

IC 74LS90 dan 7493 adalah counter asinkron yang menghitung pulsa clock dengan jumlah maksimum berbeda: 74LS90 hingga 9 (1001) dan 7493 hingga 15 (1111). Keduanya memiliki input clock (CK A dan CK B), output biner (Q0-Q3 atau QA-QD), serta pin reset (R0 dan R9). Untuk mereset, logika 1 harus diberikan ke kedua pin reset; R0 mengatur output menjadi 0, sedangkan R9 pada 74LS90 mengatur output menjadi 9.

Pada percobaan, jika clock A dan B diparalelkan seperti pada 2a, output menjadi tidak beraturan karena pulsa diterima bersamaan. Hal ini mencerminkan sifat counter asinkron, di mana tahap hitungan berikutnya dipicu oleh output tahap sebelumnya.

Perbedaan ini menunjukkan pentingnya konfigurasi clock untuk mengatur pola hitungan. Reset manual memungkinkan fleksibilitas dalam memulai atau mengatur ulang hitungan, menjadikan kedua IC ini ideal untuk berbagai aplikasi rangkaian digital.

5. Video Rangkaian [Kembali]

Tidak ada komentar:

Posting Komentar